S R Latch Notes

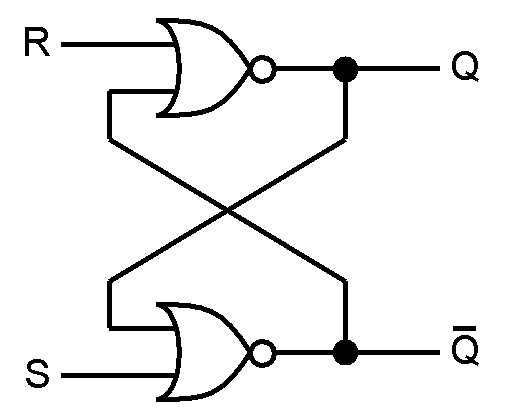

Chapter 7 – Latches and Flip-Flops Page 3 of 18 a 0. When both inputs are de-asserted, the SR latch maintains its previous state. Previous to t1, Q has the value 1, so at t1, Q remains at a 1. Similarly, previous to t3, Q has the value 0, so at t3, Q remains at a 0. If both S' and R' are asserted, then both Q and Q' are equal to 1 as shown at time t4.If one of the input signals is. 5.2.6 shows a timing diagram describing the action of the basic RS Latch for logic changes at R and S. At time (a) S goes high and sets Q, which remains high until time (b) when S is low and R goes high, resetting Q. During period (c) both S and R are high causing the non-allowed state where both outputs are high.

Skip to episode playlistSr Latch Schematic

Let’s talk about how memory works. If you’re geeky, then this episode is for you. You’ll look at the S-R Latch as it handles the basics of the memory circuit.

Your key takeaways in this episode are:

- The S-R Latch is a flip-flop circuit

- Uses 2 NOR gates

- The S-R Latch is one bit of memory

- Set is “true” -> stores 1

- Reset is “true” -> stores 0

Study Notes

We’ve been talking bits, bytes, 1s, 0s…but how does a computer actually retain memory? It retains memory one bit at a time, using an S-R Latch.

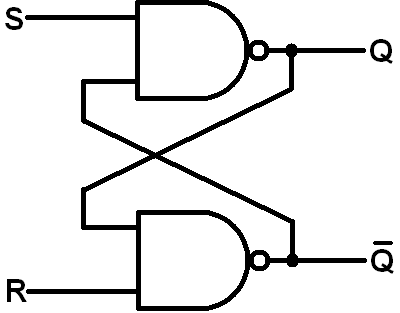

Imagine we have the gate circuit shown below. Let’s look at what is going on. We have:

- Two switches. We use these pictures of toggle switches because we’re used to seeing them and they help us visualize the “state” of something. These switches are actually outputs coming from other gate circuits, located upstream.

- Two NOR gates

- S (set) NOR gate

- R (reset) NOR gate

- Q-bar: on the S side, we have Q-bar

- Q: on the R side, we have Q, which is the opposite state of Q-bar

Set Memory

Now let’s walk through what’s happening in the wiring above.

- On the S side, we have power going through the switch and into the S NOR gate (so we have a 1.) Since the other input to the S NOR gate is also on (another 1), when the output goes through the inverter, it becomes a 0.

- The output from this S NOR gate (0) becomes an input to the R NOR gate. (Note: Since the output from the R NOR gate is an input to the S NOR gate and vice-versa, it is called a flip-flop.)

- So the R NOR gate receives that input (0) from the S NOR gate, and since the power going through the switch and into the R NOR gate is also a 0, that means both inputs are 0s. When the output from the R NOR gate goes through the inverter, it is changed to an on state, or 1. (This is where the S NOR gate gets its second input that we mentioned in Step 1 above.)

- Q is where the memory is being stored. In this particular diagram, Q stores one bit of memory, and its value is a 1. (The light bulb here is only used to help with visualization.)

Reset Memory

During the reset, the circuit is storing a 0, which resets the memory state held in Q.

NOR Gate Cheatsheet

Remember your NOR Gate cheat sheet? Here it is again, in case you need a refresher after reading about the wiring above.

Sr Latch Example

NOR Gate

| Switch 1 (in1) | Switch 2 (in2) | Light bulb (out) |

|---|---|---|

| 1 | 1 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 0 | 0 | 1 |

Your best friend is code, Tonya is making the introductions.

Episodes

Total Lab Runtime: 01:53:22

- 1Lab Introductionfree02:20

- 2Understanding Switch Logicfree13:36

- 3Introduction to Pseudocode and Truth Tablesfree16:28

- 4Understanding Gates – NOT Gatefree10:10

- 5Understanding Gates – AND Gatefree15:07

- 6Understanding Gates - OR Gatefree10:33

- 7Understanding Gates – XOR Gatefree10:42

- 8Understanding Gates – NAND Gatefree07:10

- 9Understanding Gates – NOR Gatefree06:34

- 10Basics of Memory Circuit – S-R Latchfree04:41

- 11Basics of the Adder Circuitfree16:01

Back to the lab's opening page.

Back to the lab's opening page.Sr Latch Notes Book

I am thinking of some kind of fault circuit, but I would like to consult you about whether it is useful or not.

As an example, consider a kind of circuit, and this circuit contains fault detection circuits in various parts. For example; over temperature, humidity, over current / voltage etc. I plan to apply it to the inputs of an S / R Latch IC when any malfunction like these is detected. The outputs of the Latch IC will be interconnected with the OR gate. Thus, in case of any malfunction, whatever malfunction occurs, the S / R latch output will be 1 and the output of the OR gate will also be 1. The output of the OR gate will also be connected to the interrupt pin of a microcontroller, and it will stop the operation of the system safely. The reset of the S / R latch will be provided by the user pressing the button on the card or by an external controller. In this way, the output of the OR gate will be 0 and the microcontroller will control the system again.

Do you think this idea is useful? What would you suggest me?